# **Design of Digit Serial FIR Filter**

Ms. Sneha Bire and Mrs. Mamta Sarde

Dept. of Electronics (Communication) Abha Gaikwad– Patil College of Engineering & Technology Nagpur, India E-mail: biresneha@gmail.com, msarde@gmail.com

#### Abstract

In the last two decades, many efficient algorithms and architectures have been introduced for the design of low complexity bit-parallel multiple constant multiplications (MCM) operation which dominates the complexity of many digital signal processing systems. On the other hand, little attention has been given to the digit-serial MCM design that offers alternative low complexity MCM operations albeit at the cost of an increased delay. In this paper, we address the problem of optimizing the gate-level area in digit-serial MCM designs and introduce highlevel synthesis algorithms, design architectures, and a computer aided design tool. Experimental results show the efficiency of the proposed optimization algorithms and of the digit-serial MCM architectures in the design of digit-serial MCM operations and finite impulse response filters.

#### 1. Introduction

Finite impulse response (FIR) filters are widely used in digital signal processing applications due to their stability and linear phase characteristics. FIR filters have a large number of multiplications involved in the filter algorithm, which are usually implemented using fixed-point or integer number representations with the filter coefficients being represented by a finite number of bits. In hard-wired ASIC designs, multiplication operations are replaced by shift-and-add operations towards multiplier less FIR filter design. From a power perspective, the fewer the number of adders, the less power the filter will consume.

The most common approaches to the implementation of digital filtering algorithms are general purpose digital signal processing chips for audio applications, or special purpose digital filtering chips and application-specific integrated circuits (ASICs) for higher rates. This project describes an approach to the implementation of digital filter algorithms on field programmable gate arrays (FPGAs). Recent advances in FPGA technology have enabled these devices to be applied to a variety of applications traditionally reserved for ASICs. FPGAs are well suited to data path designs, such as those encountered in digital filtering applications. The density of the new programmable devices is such that a nontrivial number of arithmetic operations such as those encountered in digital filtering may be implemented on a single device. The advantages of the FPGA approach to digital filter implementation include higher sampling rates than are available from traditional DSP chips, lower costs than an ASIC for moderate volume applications, and more flexibility than the alternate approaches

#### 2. System Objective

The impulse response  $\hbar[n]$  can be calculated if we set  $x[n] = \delta[n]$  in the above relation, where  $\delta[n]$  is the Kronecker delta impulse. The impulse response for an FIR filter then becomes the set of coefficients  $b_n$ , as follows

$$h[n] = \sum_{i=0}^{n} b_i \delta[n-i] = b_n$$

for n = 0 to N.

- i. Plateform, Tools & Techniques

- ii. MATLAB 7.3 (R2006B)

- iii. Aldec Active HDL

- iv. Quartus II

#### 3. Filter Realization

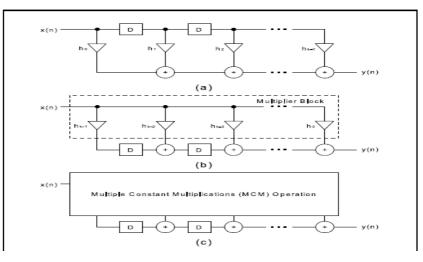

**Fig. 5:** FIR filters implementations(a) Direct form. (b) Transposed form with generic multipliers. (c) *Transposed form with an MCM block*.

The direct and transposed-form FIR filter implementations are illustrated in Fig. 5(a) and 5(b), respectively. The multiplier block of the digital FIR filter in its transposed form [Fig. 5(b)], where the multiplication of filter coefficients with the filter input is realized, has significant impact on the complexity and performance of the design because a large number of constant multiplications are required. This is generally known as the multiple constant multiplications (MCM) operation. The goal is the minimization of nonzero terms within the discrete coefficients as each nonzero term corresponds to an additional adder in the hardware implementation. Depending on the target hardware, it may be possible to implement a linear-phase FIR filter using less multipliers than the minimum-phase filter by taking advantage of the symmetry even if the filter length of the linear-phase is larger.

#### 4. Design Implementation

In direct form structure even though there are only two multipliers, there are still three delays (same as for the direct-form structure) required since the number of delays corresponds to the order of the filter. The direct-form structure has the disadvantage that each adder has to wait for the previous adder to finish before it can compute its result. For high speed hardware such as FPGAs/ASICs, this introduces latency which limits how fast the filter can be clocked.

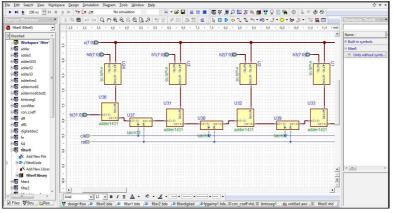

A solution to this is to use the transposed direct-form structure instead. With this structure, the delays between the adders can be used for pipelining purposes and therefore all additions/multiplications can be performed in fully parallel fashion. This allows real-time handling of data with very high sampling frequencies.

#### **Direct Form Structure**

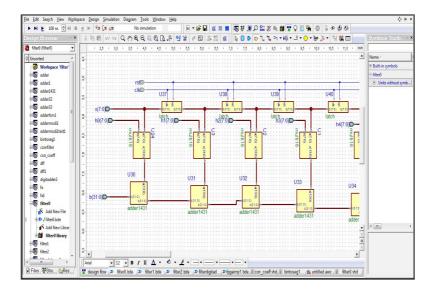

Fig. 1: Direct form of FIR filter.

## **1.2 Transpose form Structure**

Fig. 2: Transpose form of FIR filter using Active HDL

## **1.3 Optimized Structure**

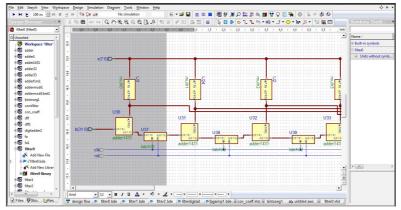

Fig. 3: Optimized Form of FIR filter using Active

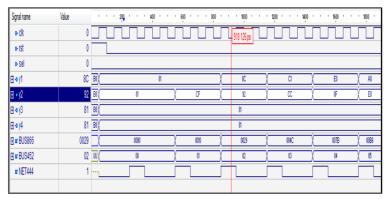

## Output Wave form of Filter 1 & Filter

Fig. 4: Output Wave form of Filter 1 & Filter 2

## **Result Verification Through MATLAB**

| MATLAS 7.10.0 (R2010  | )                                    |                       | -                  | -                |      |       |    | ×     |

|-----------------------|--------------------------------------|-----------------------|--------------------|------------------|------|-------|----|-------|

| ile Edit Debug Par    | allel Desktop I                      | Window Help           |                    |                  |      |       |    |       |

| 00 8 8 8 5            | ( ) d =                              | Current F             | older: Nk\dsp proj | ect/Matlab files | -    | 0     |    |       |

| Shertcuts I How to Ad | d 🕑 What's New                       |                       |                    |                  |      |       |    |       |

| Command Window        |                                      |                       |                    |                  |      |       |    | E * . |

| New to MATLAB? Watc   | h this <u>Video</u> , see <u>D</u> a | ernos, or read Gettin | ng Started.        |                  |      |       |    |       |

| >> x=[1 2 3 4 5       | 6789]                                |                       |                    |                  |      |       |    |       |

| x =                   |                                      |                       |                    |                  |      |       |    |       |

| x -                   |                                      |                       |                    |                  |      |       |    |       |

| 1 2                   | 3 4                                  | 5 6                   | 7 8                | 9                |      |       |    |       |

|                       |                                      |                       |                    |                  |      |       |    |       |

| >> h=[16 9 10 1       | 2 12 9 1 16 8                        | 1 81 16 1 9 :         | 12 12 10 9 10      | 5]               |      |       |    |       |

| h =                   |                                      |                       |                    |                  |      |       |    |       |

|                       |                                      |                       |                    |                  |      |       |    |       |

| Columns 1 thr         | ough 15                              |                       |                    |                  |      |       |    |       |

| 16 9                  | 10 12                                | 12 9                  | 1 16 6             | 81 81            | 16 1 | 9 12  | 12 |       |

| Columns 16 th         | rough 18                             |                       |                    |                  |      |       |    |       |

| 10 9                  | 16                                   |                       |                    |                  |      |       |    |       |

| >> y=conv(x,h);       |                                      |                       |                    |                  |      |       |    |       |

| >> 7                  |                                      |                       |                    |                  |      |       |    |       |

| y =                   |                                      |                       |                    |                  |      |       |    |       |

| y -                   |                                      |                       |                    |                  |      |       |    |       |

| Columns 1 thr         | ough 7                               |                       |                    |                  |      |       |    |       |

|                       | 20                                   | 100                   | 1000               | 10000            |      | 10110 |    |       |

| 16                    | 41                                   | 76                    | 123                | 182              | 250  | 319   |    |       |

| Columns 8 thr         | bugh 14                              |                       |                    |                  |      |       |    |       |

| 404                   | 570                                  | 657                   | 814                | 953              | 1071 | 1189  |    |       |

Fig. 5: Result Verification through MATLAB.

# 5. ARESULT

## 5.1 Compilation Report of Filter 1 and Filter 2

**Table 1:** Compilation Summary of Filter 1 and Filter 2

| Specifications       | Filter 1      | Filter 2     |

|----------------------|---------------|--------------|

| Entity Name          | Fpgaimp1      | Fpgaimp2     |

| Family               | Cyclone       | Cyclone      |

| Device               | EPIC6Q240C7   | EPIC6Q240C7  |

| Total logic elements | 508/5980 (8%) | 492/5980(8%) |

| Total Pins           | 51/185(28%)   | 20/185(11%)  |

## Power Optimization Report of Filter 1 and Filter 2

| Table 2: Power | Comparison | Of Filter 1 | & Filter |

|----------------|------------|-------------|----------|

|                | comparison |             |          |

| Specification                          | Filter 1  | Filter 2  | Power<br>Optimized |

|----------------------------------------|-----------|-----------|--------------------|

| Total thermal Power dissipation        | 133.81 mW | 104.44 Mw | 21.949%            |

| Core Dynamic thermal Power dissipation | 7.87 mW   | 5.94 mW   | 24.523%            |

| Core Static thermal Power dissipation  | 60.00 mW  | 60.00 mW  | 0                  |

| I/O thermal Power dissipation          | 65.94 mW  | 38.49 mW  | 41.628%            |

#### References

- [1] Aksoy, C. Lazzari, E. Costa, P. Flores, and J. Monteiro, "Efficient shift-adds design of digit-serial multiple constant multiplications," in *Proc. Great Lakes Symp. VLSI*, 2011, pp. 61–66.

- [2] Mustafa Aktan, Arda Yurdakul, and Günhan Dündar, "An Algorithm for the Design of Low-Power Hardware-Efficient FIR Filters" IEEE trans. on circuits and systems-I,VOL. 55, NO. 6, JULY 2008.

- [3] Speak & Spell, the First Use of a Digital Signal Processing IC for Speech Generation, 1978". *IEEE Milestones*. IEEE. Retrieved 2012-03-02.

- [4] Bogdanowicz, A. (2009-10-06). "IEEE Milestones Honor Three". *The Institute*. IEEE. Retrieved 2012-03-02.

- [5] L. Aksoy, E. Costa, P. Flores, and J. Monteiro, "Exact and Approximate Algorithms for the Optimization of Area and Delay in Multiple Constant Multiplications," IEEE TCAD, vol. 27, no. 6, pp. 1013-1026,2008.

- [6] H. Nguyen and A. Chatterjee, "Number-Splitting with Shift-and-Add Decomposition for Power and Hardware Optimization in Linear DSP Synthesis," IEEE Trans. on VLSI, vol. 8, no. 4, pp. 419--424, 2000.

- [7] Dempster and M. Macleod, "Use of Minimum-Adder Multiplier Blocks in FIR Digital Filters," IEEE TCAS II, vol. 42, no. 9, pp. 569-577, 1995.

- [8] Y. Voronenko and M. Piischel, "Multiplierless Multiple Constant Multiplication," ACM Transactions on Algorithms, vol. 3, no. 2, 2007.

- [9] R. Hartley and K. Parhi, *Digit-Serial Computation*. Norwell, MA: Kluwer, 1995.

- [10] M. Aktan, A.Yurdakul, and G. Dundar, "An algorithm for the design of lowpower hardware-efficient FIR filters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 55, no. 6, pp. 1536–1545, Jul. 2008.

- [11] J. B. Evans, Y. C. Lim, and B. Liu. A high speed programmable digital FIR filter. In *IEEE Int. Conf. Acoust., Speech, Signal Processing*, Apr 1990.

- [12] R. Hartley, P. Corbett, P. Jacob, and S. Karr. A high speed FIR filter designed by compiler. In *IEEE Cust. IC Conf.*, pages 20.2.1–20.2.4, May 1989.