# Comparison of Sinusoidal Pulse Width Modulation based Seven and Five Level Cascaded Inverters

<sup>1</sup> M.Murugesan, <sup>2</sup>R.Sakthivel, <sup>3</sup>D.Pushpalatha and <sup>4</sup>R.Pari

1, 2, 3, 4- Faculty of Electrical and Electronics Engineering V.S.B Engineering College, Karur, Tamilnadu, India.

#### Abstract

In this paper, new reduced switch count technique is introduced to construct a multilevel inverter topology which reduces the number of switches used in the system. Sinusoidal pulse width modulation is used to control proposed inverter. In conventional H-bridge multilevel inverter to produce a seven level ten number of switches are used. Due to involvement of high number of switches thereby the harmonics, switching losses, cost and the total harmonics distortion is increased. This proposed topology involves only eight number of switches. It dramatically reduces the switches for high number of levels that reduces the switching losses; cost and low order harmonics and thus effectively decreases total harmonics distortion.

*Keywords*— cascaded multilevel inverter, H-bridge multilevel inverter, THD, PWM, IGBT, Multilevel Inverter (MLI).

### **INTRODUCTION**

A multilevel inverter is a power electronic converter built to synthesize a desired AC voltage from several levels of DC voltages which the DC levels were considered to be identical in that all of them were batteries, solar cells, capacitors, etc. The multilevel inverter has gained much attention in recent years due to its advantages in lower switching loss better electromagnetic compatibility, higher voltage capability, and lower harmonics [1]-[3]. Several topologies for multilevel inverters have been proposed; the most popular being the diode-clamped [4], [5], flying capacitor [6], and cascade H bridge [7] structures. Besides the three basic multilevel inverter topologies; other multilevel converter topologies have been proposed, most of these are hybrid circuits that are combinations of two of the basic multilevel topologies. The main disadvantage still exists in diode clamped multilevel inverter topology, which restricts the use of it to the high power range of operation. The first topology introduced is the

series H-bridge design [1] in which several configurations have been obtained. An apparent disadvantage of this topology is the large number of isolated voltage required to supply each cell. In this proposed topology three H- Bridges are combinely connected together to form a seven level inverter. The proposed topology for multilevel inverter has a high number of steps associated with a low number of power switches. In addition for producing all the levels (odd and even) at the output voltage, a procedure for calculating the required dc voltage source is proposed. In this topology pulse width modulation technique is used. The THD will be decreased by increasing the number of levels. It is obvious that an output voltage with low THD is desirable, but increasing the number of levels needs more hardware, also the control will be more complicated. It is a tradeoff between price, weight, complexity and a very good output voltage with lower THD.

#### **II.CASCADED H-BRIDGE MULTILEVEL INVERTER**

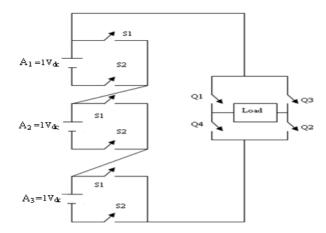

The general structure of the conventional cascaded multilevel inverter is shown in figure 1. Each of the separate voltage source  $(A_1, A_2, A_3)$  connected in cascade with other sources via a special circuit associated with it. Each stage of the circuit consists of only two active switching elements that can make the output voltage source only in positive polarity with several levels; or it can be simply zero volts depending on the switching condition of the switches in the circuit [6].

Figure 1. Topology of Hybrid Multilevel Inverter with reduced number of switches

Only one H-bridge is connected to get both positive and negative polarity. The main advantages of this hybrid multilevel inverter are high number of levels with reduced number of bridges and dc sources. The S number of dc source or stages and the associated number output level can be calculated by using the equation

$N_{level} = 2S + 1 \tag{1}$

For example if S=3, the output wave form has 7 levels ( $\pm 7, \pm 6, \pm 5, \pm 4, \pm 3, \pm 2, \pm 1$

and 0) which is shown in the figure 17 and voltage on each stage can be calculated by using the equation

$$A_i = 1V_{dc} (i=1, 2, 3...)$$

(2)

The number switches used in this topology is given by the equation N switch=2S + 4

# **III. MODIFIED CASCADED MULTILEVEL INVERTER**

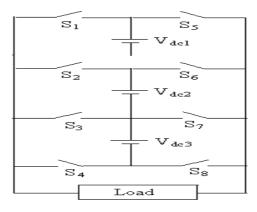

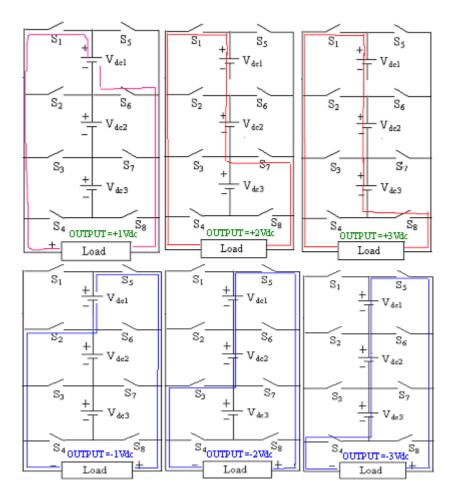

The general structure of the modified cascaded multilevel inverter is in Figure 2. Each of the separate voltage source ( $V_{dc1}$ ,  $V_{dc2}$ ,  $V_{dc3}$ ) connected with three H-bridges which are connected together. The operation of modified cascaded multilevel inverter is shown in figure 4. From this diagram when  $S_1$  and  $S_6$  is turn on the voltage across the load is  $+1V_{dc}$ . To get second step ( $+2V_{dc}$ ) switch  $S_6$  should be turned off and switch  $S_7$  has to be turned on. Similarly the negative half cycle steps can be obtained by keeping  $S_5$  in on state throughout the entire half cycle and the steps  $-1V_{dc}$ ,  $-2V_{dc}$ ,  $-3V_{dc}$  can be obtained by properly turning on the  $S_2$ ,  $S_3$  and S4 respectively. The main advantages of hybrid multilevel inverter are high number of levels with reduced number of bridges and dc sources. The S number of dc source or stages and the associated number output level can be calculated by using the equation

$N_{level} = 2S + 1 \tag{4}$

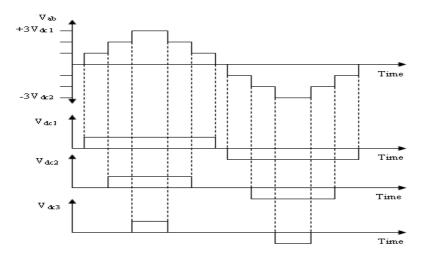

For example if S=3, the output wave form has 7 levels  $(\pm 3, \pm 2, \pm 1 \text{ and } 0)$  which is shown in the Figure 3 and voltage across the capacitor (S) on each stage can be calculated by using the equation

$$A_i = 1V_{dc} (i = 1, 2, 3....)$$

(5)

Figure 2. Topology of Modified Cascaded Multilevel Inverter

The number of switches used in this topology is given by the equation  $N_{switch}=4S+2$

(3)

(6)

Figure 3. Typical Output Voltage Waveform for Modified Cascaded Multilevel Inverter

Figure 4. Operation Diagram of Modified Hybrid Multilevel Inverter

#### **V. PWM FOR HARMONICS REDUCTION**

PWM technique is extensively used for eliminating harmful low-order harmonics in inverters. In PWM control, the inverter switches are turned ON and OFF several times during a half cycle and output voltage is controlled by varying the pulse width. SPWM techniques are characterized by constant amplitude pulses with different duty cycle for each period. The width of this pulses are modulated to obtain inverter output voltage control and to reduce its harmonic content. Sinusoidal pulse width modulation is the mostly used method in motor control and inverter application [7]. In order to verify the ability of the proposed multilevel inverter topology to synthesize an output voltage with a desired amplitude and better harmonic spectrum, programmed SPWM technique is applied to determine the required switching angles. It has been proved that in order to control the fundamental output voltage and eliminate 'n' harmonics, 'n+1' equations are needed. The method of elimination will be presented for 7-level inverter such that the solution for three angles is achieved. The Fourier series expansion of output voltage waveform using fundamental frequency switching scheme as follows

$$V_o(\omega t) = \sum_{n=1,3,5}^{\infty} \frac{4V_{dc}}{n\pi} (\cos(n\theta_1)) + \cos(n\theta_2) + \dots + \cos(n\theta_K)) \sin(n\omega t)$$

(6)

Where K is the number of switching angle required for 7 level inverter. Ideally, for a given fundamental voltage  $V_1$ , it is required to determine the switching angles $\theta_1, \theta_2, ..., \theta_K$  so that output voltage  $V_0(\omega t)=V_1\sin(\omega t)$  and a specific higher harmonics of  $V_n(n \omega t)$  are equal to zero. According to the three phase theory in balanced three phase system third order harmonic is cancelled. The switching angles can be found by solving the following equations

$$\cos(\theta_1) + \cos(\theta_2) + \cos(\theta_3) = m$$

$$\cos(5\theta_1) + \cos(5\theta_2) + \cos(5\theta_3) = 0$$

$$\cos(7\theta_1) + \cos(7\theta_2) + \cos(7\theta_3) = 0$$

(7)

Where modulation index,  $m = \frac{V_1}{(\frac{4Vdc}{\pi})}$

One approach to solve theset of nonlinear transcendental equations (9), is to use an iterative method such as the Newton-Raphson method [8]. In contrast to iterative methods, the approach here is based on solving polynomial equations using the theory of resultants which produces all possible solutions [9]. The transcendental equations characterizing the harmonic content can be converted into polynomial equations. Then the resultant method is employed to find the solutions when they exist. These sets of solutions have to be examined for its corresponding total harmonic distortion (THD) in order to select the set which generate the lowest harmonic distortion (mostly due to the 11<sup>th</sup> and 13<sup>th</sup> harmonics). The computed THD in percent is defined by

$$THD\% = \frac{\sqrt{V_3^2 + V_5^2 + V_7^2 + \dots + V_{19}^2}}{V_1^2} \times 100$$

(8)

Transforming the transcendental equations (9) into polynomial equations using the change of variables and the trigonometric identities

$\begin{aligned} x_1 &= \cos \theta_1, x_2 &= \cos \theta_2, \ x_3 &= \cos \theta_3, x_4 &= \cos \theta_4, \\ x_5 &= \cos \theta_5, \ x_6 &= \cos \theta_6, \ x_7 &= \cos \theta_7 \end{aligned}$  (9)

$\ddot{\cos(5\theta)} = 5\cos\theta - 20\cos^3\theta + 16\cos^5\theta$  $\cos(7\theta) = -7\cos\theta + 56\cos^3\theta - 112\cos^5\theta + 64\cos^7\theta$ (10)

$$\cos(7\theta) = -7\cos\theta + 50\cos^2\theta - 112\cos^2\theta + 64\cos^2\theta$$

To transfer (9) into the equivalent conditions

$$p_{1}(x) = x_{1} + x_{2} + x_{3} + -m = 0$$

$$p_{5}(x) = \sum_{i=1}^{7} (5x_{i} - 20x_{i}^{3} + 16x_{i}^{5}) = 0$$

$$p_{7}(x) = \sum_{i=1}^{7} (-7x_{i} + 56x_{i}^{3} - 112x_{i}^{5} + 64x_{i}^{7}) = 0$$

(11)

System (12) is a set of three polynomial equations in three unknowns  $x_1$ ,  $x_2$ , and  $x_3$ , where  $x=(x_1, x_2, x_3, )$  and the angles condition must satisfy  $0 \le x_1 \le x_2 \le x_3 \le 1$ . Polynomial systems are also considered to compute the solutions of the harmonic elimination equations by iterative numerical methods which give only one solution [10]. In contrast, this system of polynomial equations will be solved using resultant such that all possible solution of (9) can be found. A systematic procedure to do this is known as elimination theory and uses the notion of resultants. The details of this procedure can be found in [10].

## VI. TOTAL HARMONICS DISTORTION (THD)

In order to determine the relative distortion due to harmonics on a power system, the term total harmonic distortion has emerged. Total harmonic distortion is a measure of the amount of distorted harmonics that are impeged on the system voltage, expressed as a percentage of the fundamental. Both voltage and current waveform distortion are represented by THD.

$$THD = \sqrt{\frac{\text{sum of squares of amplitude of all harmonics}}{\text{square of amplitude of fundamental}}} X 100\%$$

(12)

## VII. SIMULATION RESULT ANALYSIS

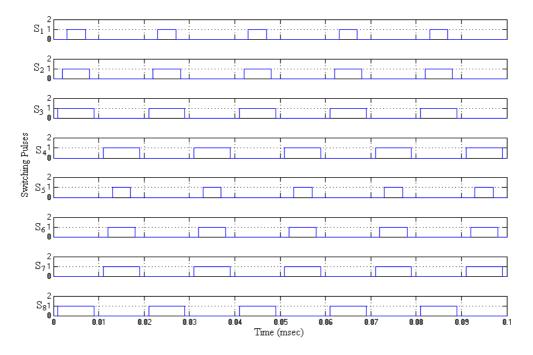

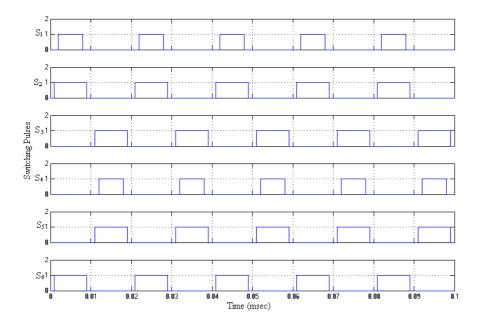

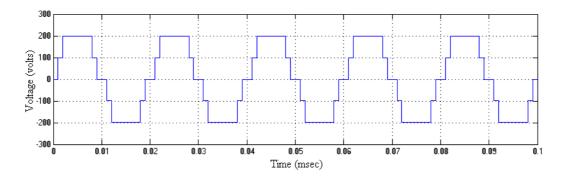

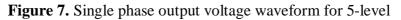

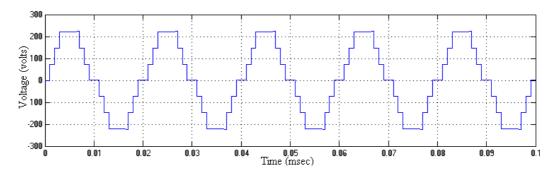

The performance of the proposed modified hybrid multilevel inverter for R-load is verified through the simulation results. An input voltage for each succeeding voltage source is  $1V_{dc}$ . The total rms voltage for single phase is 228 V for seven levels. The switching pulses for five and seven level are shown in figure 5 and figure 6 respectively.

Figure 5. Switching pulses of Switches  $S_1$ ,  $S_2$ ,  $S_3$ ,  $S_4$ ,  $S_5$ ,  $S_6$ ,  $S_7$  and  $S_8$  for Seven Level

Figure 6. Switching pulses of Switches S1, S2, S3, S4, S5 and S6 for Five Level

Figure 8. Single phase output voltage waveform for 7-level

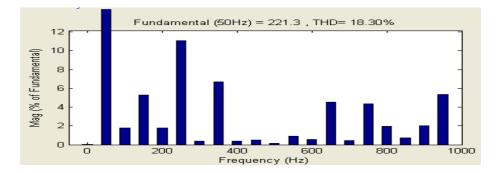

Figure 9. FFT analysis for 15-level Modified Hybrid Multilevel inverter

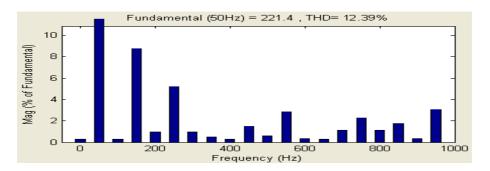

Figure 10. FFT analysis for 15-level Modified Hybrid Multilevel inverter

Figure 7 and Figure 8 shows the MATLAB single phase simulation output voltage wave form five and seven level. From figure 9, THD value of five level inverter is 18.30% and figure 10, THD value of seven level inverter is 12.39%. From the FFT analysis window when the numbers of levels are increased, the harmonics and total harmonic distortion is reduced. Table 1. Shows the comparison of THDs and Number of switches for five and seven level inverter

| S.No | Level | THD (%) | Number of Switches Involved |          |

|------|-------|---------|-----------------------------|----------|

|      |       |         | Conventional                | Proposed |

| 1    | Five  | 18.30   | 8                           | 6        |

| 2    | Seven | 12.39   | 10                          | 8        |

Table 1. Comparison of Total Harmonic Distortion

### **VIII. CONCLUSION**

This paper has demonstrated the state of the art of modified multilevel inverter topology with reduced number of switches. This multilevel inverter structure and its basic operations have been discussed. A procedure for calculating the required voltage level on each stage has been described. In the conventional methods as the number of levels are increased the required number of switches also increased. Due to involvement of high number of switches thereby increasing the harmonics, switches losses, cost and the total harmonics distortion the proposed method dramatically reduces the switches for high number of levels. But the proposed topology involves considerably less number of switches for higher levels.

### REFERENCE

- [1] Peng, F. Z. and Lai, J. S., Lai, J. S., McKeever, J. W. and VanCoevering, J. A., 1996, "Multilevel voltage source inverter with separate DC sources for static var generation", IEEE Trans. Ind. Appl., Vol. 32, No. 5, pp. 1130–1138, Sept./Oct.

- [2] Tolbert, L. M. and Peng, F. Z., 1999, "Multilevel converters for large electric drives", IEEE Trans. Ind. Appl., Vol. 35, No. 1, pp. 36-34, Jan./Feb.

- [3] Corzine K. A, Wielebski M. W, Peng F. Z., and Wang J., 2004, "Control of Cascaded Multilevel Inverters," *IEEE Trans. power electron*, vol.19, no.3, pp. 732-738, May.

- [4] Fracchia M., Ghiara T., Marchesoni M., and Mazzucchelli M., 1992, "Optimized modulation techniques for the generalized N-level converter," *in proc. IEEE power electronics specialist conf*, 1205-1213, *Madrid*, Spain.

- [5] Corzine K. A. and Baker J. R., 2002, "Reduced parts-count multilevel rectifiers," "*IEEE Trans. Ind. Electron.*" vol.49, no.3, pp. 766-774, Aug.

- [6] Peng F. Z., 2004, "A generalized multilevel inverter topology with self voltage balancing," "*IEEE Trans. Ind. Applica*," vol. 37, pp.611- 618, Mar./April.

- [7] Manjrekar M. D., Steimer P. K., and Lipo T. A., 2000, "Hybrid multilevel power conversion system: a competitive solution for high- power applications, "*"IEEE Trans. Ind. Applica*, " vol. 36, pp. 834-841, May/June.

- [8] Ismail, S. T., 2006, "Development of a Single Phase SPWM Microcontroller-Based Inverter" First International Power and Energy Conference PEC, Putrajaya, Malaysia: IEEE, Nov, 28-29,

- [9] Patel H.S., and Hoft R.G., 1973, "Generalized Techniques of Harmonic Elimination and Voltage Control in Thyristor Inverters: Part I Harmonic Elimination", IEEE Trans. Ind. Appl., 3, pp. 310-317.

- [10] Chiasson J.N., Tolbert L.M., Mckenzie K.J. and Du Z., "Control of a Multilevel Converter Using Resultant Theory", IEEE Transactions Control System Theory, Vol. 11, No.3, pp. 345-354, 2003.\*

## BIOGRAPHY

**M.Murugesan** was born in Anthiyur on December 27, 1986. He is graduated in Electrical and Electronics engineering in 2009 from Anna University, Chennai. He is post graduated M.E Power Electronics and Drives during 2011 from Anna University. He is currently working as Assistant professor at V.S.B Engineering College. His area of interest involves in Power Electronics, inverter, modeling of induction Motor. He is an Indian Society for Technical Education (ISTE) life member. He has published more than 15 papers.

**R.Sakthivel** received his Bachelor degree in Electrical and Electronics engineering from Madras University, Chennai, in the year 2002, and Masters in power electronics and drives from Anna University, Chennai in the year 2007. He is currently working as a Assistant professor in the Department of Electrical and Electronics Engineering, at V.S.B. Engineering college, Karur. His research area includes Semiconductor devices, Inverters, Machine design and Drives & controls.

**D.Pushpalatha** was born in Karur on June 13, 1986. She is graduated in Electrical and Electronics engineering in 2008 from Anna University, Chennai. She is post graduated M.E Applied Electronics during 2012 from Anna University. She is currently working as Assistant professor at V.S.B Engineering College. Her area of interest involves in Power Electronics, converter and inverter, modeling of drives. She is an ISTE life member. She has published more than 5 papers in various national/international conference and journals.

**R.Pari** was born in Karur on June 13, 1987. He is graduated in Electrical and Electronics engineering in 2008 from Anna University, Chennai. He is post graduated M.E Power Electronics and Drives during 2012 from Anna University. He is currently working as Assistant professor at V.S.B Engineering College. His area of interest involves in Power Electronics, converter and inverter, modeling of drives. He is an ISTE life member. He has published more than 5 papers in various national/international conference and journals.