# Optimized Magnetic Flip-Flop Combined With Flash Architecture for Memory Unit Based On Sleep Transistor

Malarvizhi.M<sup>1</sup>,

*l PG scholar, Applied Electronics* A.V.C College of Engineering, Mannampandal, TamilNadu, India. malarmoorthy05@gmail.com<sup>1</sup>

## Karthikeyan.T<sup>2</sup>

2 Assistant Professor, Department of Electronics and communication Engineering A.V.C College of Engineering, Mannampandal, TamilNadu, India. vtkarthi180gmail.com<sup>2</sup>

#### Abstract

The portability in the electronic circuits is achieved by the use of battery. So its make designs for low power consumption.Normally Non-Volatile Memories of STTMRAM is mainly used to designing process .Because STTMRAM have more advantages i.e., low power, infinite endurance and high speed. But STTMRAM have main disadvantage is high writable energy produced when buildup of MFF.so it's achieve high power consumption. To overcome these disadvantage of STTMRAM using the technique are swapped MOS technique. The MOS is swapped means" Exchange of Transmission". And then removal of NOR flash memory means modified the memory unit based on sleep transistor to achieved the result of reduce power consumption and also reduce the circuit complexity

Index terms: swapped MOS design, MFF, STTM RAM, sleep transistor.

#### I. INTRODUCTION

The number of flip flop or register is used for compute the advanced microprocessor. The NVM (Non-Volatile Memory) are not need power in standby mode and also easily sored to retain the data value. But the volatile memories need power in standby mode to provide high power consumption. The Spin Transfer Torque Magneto resistive RAM (STTMRAM) has been combined of both SRAM and DRAM advantages. MRAM stored only the magnetic storage value. We know that DRAM refreshes all cells in their chips. So it is need greater power consumption.

But MRAM never requires a refresh. This means that not only does it retain its memory with the power turned off but also there is no constant power-draw. But one disadvantage of MRAM is provided the read processes are not completed incorrectly and also consume more power. So we can select the spin transfer torque combined with MRAM to the process of both write and read process for maintained at low power consumption.

STTMRAM have more advantages i.e., low power, infinite endurance and high speed. An existing system, we design of ultralow power MFF by using STTMRAM. But STTMRAM have main disadvantage is high writable energy produced when buildup of MFF.so it's achieve high power consumption.

In existing system consists of the blocks as following CMOS D-latch, STTMRAM with Magnetic Flip-Flop and enable circuit. In our proposed system we are going to implement the design as Swapped MOS design our proposed design replacing the blocks are Magnetic Flip-Flop and enable circuit by sleep transistor. Hence the complexity will be reduced and also reduce the power consumption can be obtained.

## II. PROPOSED METHOD

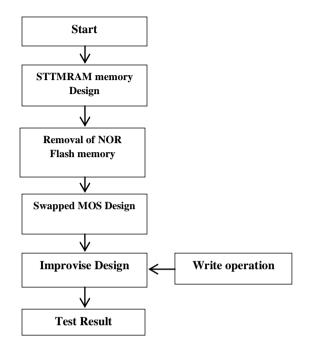

The following flow chart describes the entire architecture of this paper fig 1. First create the design of STTMRAM memory based on sleep transistor. After complete the creations of STTMARAM is built properly by using swapped MOS technique. Now these improvise design for our proposed work. This design based on sleep transistor is used for write and read operation during process with low power consumption and also reduces circuit complexity. Then finally create the layout for proposed design using T-Edit of TANNER EDA.

## A). STTMRAM

The spin transfer torque MRAM (STTMRAM) have data is stored as magnetic storage elements. These magnetic storage elements as magnetic tunnel junction (MTJ), this MTJ consist of two layers are fixed layer and free layer. The MTJ operation is based on these two layers. The STTMRAM have many advantage such as low power, high speed and without limitation of storage data. STTMRAM design memory based on sleep transistor. Sleep Transistor is circuits designed to minimize power consumption and heat dissipation. This sleep transistor avoids unwanted current received of circuit. Because it receive the current when data is needed. So easily reduce the power consumption.

**Fig1 Flow Chart for Overall Design**

# B). NOR Flash Memory

Flash memory stores information in an array of memory cells made from floating-gate transistors. Flash memory stores information in an array of memory cells made from floating-gate transistors. One limitation of flash memory is that, although it can be read or programmed a byte or a word at a time in a random access fashion, it can only be erased a "block" at a time. This NOR flash memory does not needed of error correcting code. Here using the NOR flash memory long erase and write times. It is possible to need more power, so this memory is removed to avoiding the power consumption.

# C). Swapped MOS Design

The swapped MOS design is considered as reduce the high writeable energy and reduce circuit complexity. The swapped MOS is derived of two terminal exchanges current or voltage flows of one MOS terminal to other MOS terminal. The two ends are accepted to exchange one stream of source against other stream. And also this Swapped MOS reduce internal current due to its exchange of source. Hence during low power process, stored the data and also retain data become easier.

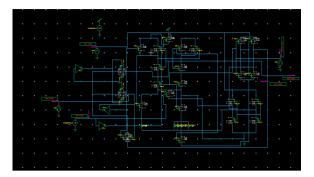

**Fig2 Overall Designs**

Before using the MFF for data storage process, but high number of bits associated the MFF, unselected cells of leakage current. In this design using of NMOS switches for neglecting of leakage current. Because here use the NMOS switches are two reference cells for even and odd bits is respectively. So t in the number of leakage current in the unselected cells is definitely neglected. The fig2 overall design are compare with existing circuit reduce the circuit complexity and power consumption are reduced.

#### D). Improvised Design

The removal of NOR flash memory for reduced the power consume. And then Swapped MOS design is based to improvise the design. Here improvise the design is already control of power consume so now applied the process of write operation to achieved of less power consume. And then here unwanted usages of circuit in existing circuits are combined with flash memory removed to reduce also the circuit complexity and improvise the speed performance.

#### **III RESULT AND DISCUSSION**

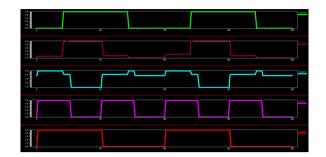

To compare the proposed output with normal CMOS DFF reduce the power consumption <780 and also reduce circuit complexity <64 and maintain the average power as <11. When voltage of write value is high (1) read the value from input of data. When voltage of write value is low (0), output of read value also low shown in fig3.

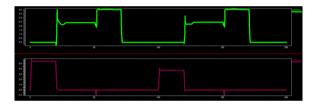

The fig4 as power consumption output waveform. The fig5 show the full layout of overall design in schematic diagram. As shown in Table 1 size of the proposed work is about <64 which is less than of existing work. Here using the number of transistor are minimum to achieving the lower area overhead (less circuit complexity).

#### Fig3 Output Waveform

#### **Table 1 power comparison of Flip-Flops**

|                                  | Proposed System | Existing System |

|----------------------------------|-----------------|-----------------|

| Lekage Power (active mode)(nw)   | 780             | 820             |

| Lekage Power (standby mode)(nw)  | 0               | 0               |

| Area (micro meter <sup>2</sup> ) | <64             | 78              |

#### **Fig4 Power Consumption Output Waveform**

**Fig 5 Layout Design**

## **IV CONCLUSSION**

In STTMRAM have one main disadvantage is high writeable energy is needed when we design of MFF. This writeable energy consumes more power hence high power consumption is occurring. The optimized design of Magnetic Flip-Flop is based on sleep transistor to reduce the power consumption. Another advantage of this technique as solves the long distortion problem during data transition and reduces the circuit complexity. For this design held in CMOS design methodology and used in Tanner EDA as simulation tool to show the performance analysis. Then finally create the layout for overall proposed design using of T-Edit in TANNER EDA.

# V REFERENCES

- 1. F.Cappello, "Fault tolerance in petascale/exascale systems: current knowledge, challenges and research opportunities," *Int. J. High Performance Comput.*, vol. 23, pp. 212-226, 2009.

- 2. G.Sun,X.Dong,Y.Xie,J.Li,andY.Chen,"Anovelarchitectureof the3DstackedMRAML2cacheforCMPs,"*Proc.HPCA2009*,pp.239–249,2009.

- 3. S.Yamamoto*etal.*,"Nonvolatilepower-gatingfield-programmable gatearrayusingnonvolatilestaticrandomaccessmemoryandnon-volatileflip-flopsbasedonpseudo-spin-transistorarchitecturewith spin-transfer-torquemagnetictunneljunctions,"*Jpn.J.Appl.Phys*,vol.51,2012.

- 4. D. Chabi, E. Deng and C. Chappert ,"Ultra Low Power Magnetic Flip-Flop Based on Check-pointing/Power Gating and Self-Enable Mechanisms",*IEEE Transactions on Circuits and Systems-I*, vol.61,n0:6, june 2014.

- 5. W.S.Zhao*etal.*, "Designconsiderationsandstrategiesforhigh-re-liableSTT-MRAM,"*Microelectron.Reliab.*, vol.51, pp.1454–1458, 2011.

- W.S.Zhao, L.Torres, Y.Guillemenet, L.-V.Cargnini, Y.Zhang, Y.Lakys, J.-O.Klein, D.Ravelosona, G.Sassatelli, and C.Chappert, "HighperformanceSoCde signusingmagneticlogicandmemory," *Proc. VLSI-SoC:AdvancedResearchforSystemsonChip, IFIPAdvancesinInformationan dCommunicationTechnology*, vol. 379, pp. 10–33, 2012, Springer.

- 7. W.S.Zhao, R.Brum, L.Torres, J.-O.Klein, G.Sassatelli, D.Ravelosona, and C.Chappert, "Spintronic memories based reconfigurable computing," *SPINJ*., 2013, to be published.

- 8. X.Wu,W.Zhao,M.Nakamoto,C.Nimmagadda,D.Lisk,S.Gu,R.Radojcic,M.N owak,andY.Xie, "Electricalcharacterizationforintertierconnectionsandtiming analysisfor3-D ICs," *IEEETrans. VeryLargeScaleIntegr.(VLSI)Syst.*,vol.20,no.1,pp.186–191,2012.

- 9. Y.Lakys,W.S.Zhao,T.Devolder,Y.Zhang,J.-O.Klein,D.Ravelosona,andC.Chappert,"Self-enabled"error-free"switchingcircuit forspintransfertorqueMRAMandlogic,"*IEEETrans.Magn.*,vol.48,pp.2403– 2406,2012.

- 10. S.Yuasa *etal.*, "Giantroom-temperaturemagnetoresistanceinsinglecrystalFe/MgO/Femagnetictunneljunctions," *Nat.Mater.*,vol.3,pp.868– 871,2004.

- 11. D. Chabi and F. Cappello" ultralow power magnetic flip flop based on check pointing/power gating and self-enable mechanism" *IEEE transaction on circuits and systems-I* regular paper vol. 60 no. 6, June 2014.

- 12. H.-P.Trinh,W. S.Zhao, J.-O. Klein,Y.Zhang, D. Ravelosona, and C.Chappert, "Magnetic Adderbased on racetrack memory," *IE EE Trans. CircuitsSyst. I, Reg. Papers*, vol. 60, pp. 1469–1477, 2013.

- 13. N.S.Kim*etal.*, "Leakagecurrent:Moore'slawmeetsthestatic power," *Computer*, vol.36, pp.68–75, 2003

- 14. InternationalRoadmapforsemiconductor(ITRS),2011ERDUpdate.

- 15. C.Chappert, A.Fert, and F.Nguyen VanDau, "Theemergenceofspin electronics indatastorage," *Nat.Mater.*, vol.6, pp.813–823, 2007.

- I.G.Baek*etal.*, "Multi-layercross-pointbinaryoxideresistive memory(OxRRAM)forpostNANDstorageapplication,"*IEDMTech.Dig.*,pp.75 0–753,December2005.

- 17. M.WuttigandN.Yamada,"Phasechangematerialsforrewriteabledatastorage,"*Nat.Mater.*,vol.6,no.11,pp.824 -832,Nov.2007.

- 18. K.Ando*etal.*, "Rolesofnon-volatiledevicesinfuturecomputer system:Normally-offcomputer," *IGIGlobal*, pp.83–107, Jun.2012.

- 19. E.Deng, Y.Zhang, J.O.Klein, D.Ravelosona, C.Chappert, and W.S.Zhao, "Low powermagnetic fulladderbasedonspintransfertor que MRAM," *IEEETrans.Magn.*, vol.49, pp.498 2–4987, 2013.

- 20. H.Yoda *etal.*, Progress of STT-MRAMTechnology and the Effecton Normally-Off Computing Systems Session 11.3, IEDM 2012.