# Performance Evaluation of Low-Power 4 X 4 Bit Memory Array Multiplier

Sunil Kumar Ojha<sup>1</sup>, O.P. Singh<sup>2</sup>, G.R.Mishra<sup>3</sup>, P.R. Vaya<sup>4</sup>

<sup>1,2,3</sup>Department of Electronics & Communication Engineering, Amity School of Engineering & Technology (ASET), Amity University, India

<sup>4</sup>Ex Prof Department of Electrical Engineering, Indian Institute of Technology Madras (IITM), India.

ORCID: 0000-0002-8969-041X (Sunil Kumar Ojha), ORCID: 0000-0002-9946-4141 (O.P Singh)

#### Abstract

For any digital integrated chip the multipliers are the basic module needed for almost all arithmetic and logic unit (ALU) application. It is used right from small multiplier circuits to huge multiprocessor design, hence since its uses are vast so the design needs to be very efficient with respect to its desired operation and also it should be capable for low power and high speed operation. This paper presents 4X4 bit binary multiplier which uses half and full adder as its circuit subsystems and to maintain low power and high speed the gate diffusion input (GDI) cells are used. The result shows the low power and high speed operation of the 4 X 4 bit binary multiplier as the proposed design consumes approximately  $9\mu$ W power with the propagation delay of nearly 18ns.

**Keywords:** Multiplier, GDI Cell, Low Power, Partial Products, MOS Characteristics.

## I. INTRODUCTION

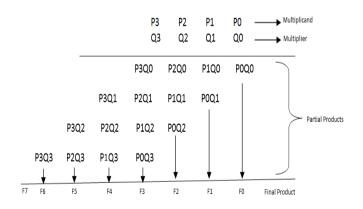

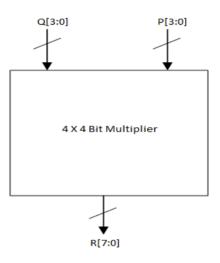

A "P X Q" multiplier can be considered as "P + Q" inputs and "P + Q" outputs as well. This device performed P bits X Q bits multiplication as shown in figure -1(a) below. The block diagram is also shown in the figure -1(b).

Figure 1(a): 4 X 4 Bit Multiplication Operation

Figure – 1(b): 4 X 4 Bit Multiplier Symbol

Here the multiplication process consist of four multiplicand bits P0, P1, P2, and P3 and four multiplier bits Q0, Q1, Q2, and Q3, partial products bits and eight finally product bits. Using AND gate the partial products are generated; and the partial product bits and the carries between the stages are indicated by XOR operation. The below calculation Shows the summation of partial products and carries required to produce the product bits for the 4 X 4 bit multiplier.

| F0 = P0Q0                              |

|----------------------------------------|

| F1 = P1Q0  xor  P0Q1                   |

| F2 = P2Q0  xor  P1Q1  xor  P0Q2        |

| F3 = P3Q0 xor P2Q1 xor P1Q2 xor P0Q3   |

| F4 = P3Q1  xor  P2Q2  xor  P1Q3        |

| F5 = P3Q2  xor  P2Q3                   |

| F6 =P3Q3                               |

| F7 = Last Carry (As per the operation) |

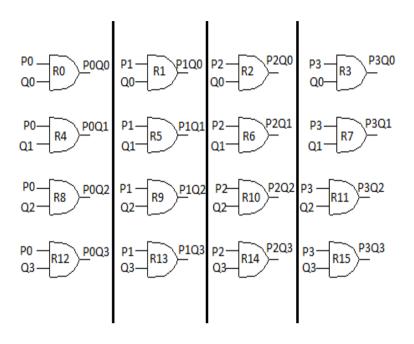

To perform the multiplication operation the partial products are generated first using AND gates as shown in figure -1(c).

Figure 1(c): Partial Product Generation

## II. PROPOSED MODEL

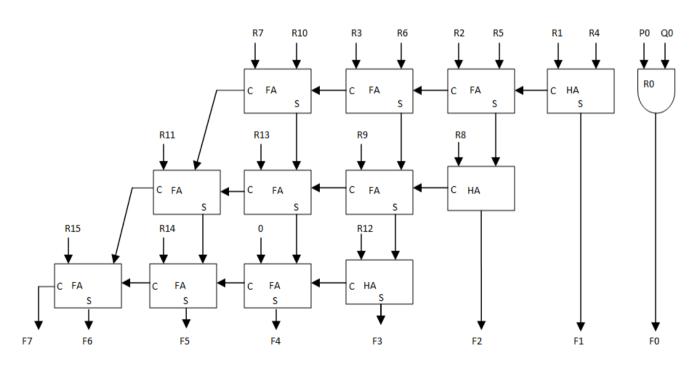

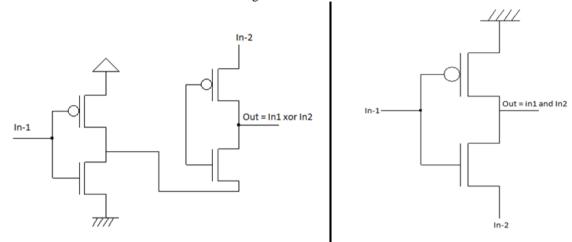

The proposed 4 X 4 bit binary multiplier is shown in figure -2(a); it consists of nine full adder and three half adder. The 4 X 4 bit binary multiplier is design hierarchically, that is first

the AND & XOR gate is designed using GDI technique, the GDI cell for AND & XOR is shown in figure -2(b).

Figure 2(a): 4 X 4 Bit Binary Multiplier

About GDI Cell: - The gate diffusion input (GDI) technique is a design methodology for low power digital circuits and systems. This technique helps in reducing propagation delay, power consumption, and also area of the digital circuits. Furthermore it also reduces the complexity of design the cell for digital circuits as less number of transistors are required as compared to conventional CMOS and transmission gate design technique. This overall results in less complex layout of the circuit which is very critical part of the IC design. The proposed 4 X 4 Bit multiplier uses this GDI technique to design the various blocks and sub-blocks at transistor level and then use them as a main circuit sub systems.

Figure 2(b): GDI Cell of AND & XOR Gate

| Device Name               | MOS Size (W/L)                               |

|---------------------------|----------------------------------------------|

| PMOS                      | 350/32                                       |

| NMOS                      | 150/32                                       |

| Supply and other Inputs   |                                              |

| VDD                       | 3.2V DC                                      |

| Inputs (all combinations) | P[3:0] (0000 to 1111), Q[3:0] (0000 to 1111) |

| Model File                | 32nm Standard Process Technology             |

**Table 1:** Simulation Conditions

### **III. SIMULATIONS AND RESULTS**

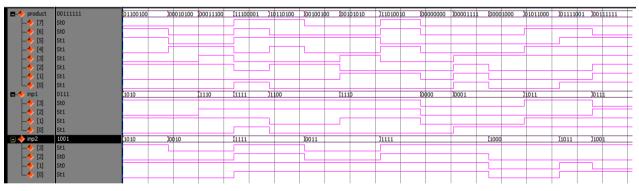

The HSPICE simulator is used for simulating the proposed model and the process technology is chosen as standard 32nm. The functionality of the 4 X 4 bit binary multiplier is verified by writing HDL code. The various parameters related to the simulation are listed in above Table -1.

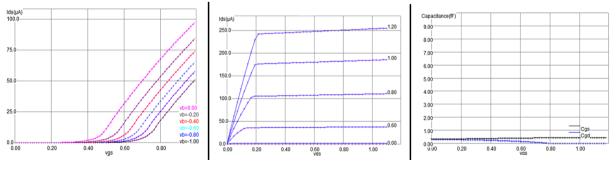

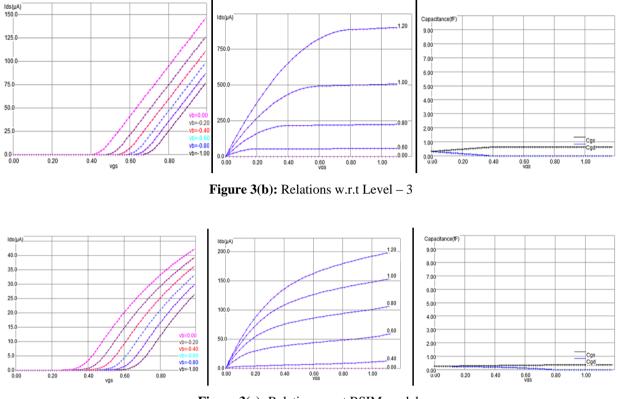

The below figure -3(a, b, and c) shows the relations between Ids vs. Vgs, Ids vs. Vgs and the parasitic capacitances. These

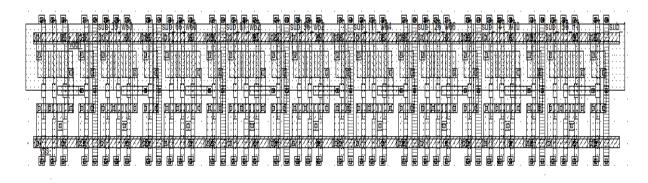

values are computed using Level -1, Level -3, and BSIM models. The results are listed in Table -2. The result shows the proper operation of 4 x 4 bit binary multiplier, and the behavior of various signal involved in the design are shown below. The figure -3(d) below shows the HDL model of 4 x 4 bit binary multiplier and it can be seen that the proposed model is working as expected. The optimized layout is shown in figure -3(e)

Figure 3(a): Relations w.r.t Level - 1

Figure 3(c): Relations w.r.t BSIM models

Figure 3(d): HDL verification of 4 X 4 Bit Binary Multiplier

Figure 3(e): Layout of 4 X 4 Bit Binary Multiplier

| Parameters                         | Values  |

|------------------------------------|---------|

| Total Average Power                | 8.37 μW |

| Cgd (Average)                      | 1.59 fF |

| Cgs (Average)                      | 1.82 fF |

| Propagation Delay                  | 18.3 ns |

| Area Optimized<br>(Using GDI Cell) | 34%     |

Table 2: Simulation Results

## IV. CONCLUSION

This paper presents  $4 \times 4$  bit binary multiplier and its working. The multiplier is designed using optimized process parameters and it is observed that the  $4 \times 4$  bit binary multiplier performs as it should and due to use of GDI cell it consumes very less power as compared to conventional CMOS. The results also reveal that the GDI cell requires less area as compared to conventional CMOS. The propagation delay also reduces in the design of half and full adders using GDI cell which helps in reducing overall delay of the multiplication operation of the  $4 \times 4$  bit binary multiplier circuit.

## REFERENCES

- [1]. R. Bala Sai Kesava et al, "Low Power and Area Efficient Wallace Tree Multiplier Using Carry Select Adder with Binary to Excess-1 Converter", Conference on Advances in Signal Processing (CASP), June 2016.

- [2]. Ismo H<sup>\*</sup>anninen et al, "Irreversible Bit Erasures in Binary Multipliers", IEEE International Symposium on Circuits and Systems (ISCAS), May 2011.

- [3]. Xiaoping Cui et al, "A Modified Partial Product Generator for Redundant Binary Multipliers" IEEE Transactions on Computers, Volume: 65, Issue: 4, pp. 1165 – 1171, April - 2016.

- [4]. Elisardo Antelo et al, "Improved 64-bit Radix-16 Booth Multiplier Based on Partial Product Array Height Reduction", IEEE Transactions on Circuits and Systems I: Regular Papers, Volume: 64, Issue: 2, pp. 409-418, Feb-2017.

- [5]. Sunil Kumar Ojha, O.P. Singh, G.R.Mishra, and P.R. Vaya, "Effect of Threshold Roll-Off on Static Noise Margin of Sram Cell", Journal of Engineering and Applied Sciences, Vol. 13, Issue 14, pp. 5801 – 5806, ISSN: 1818-7803, Year – 2018.

- [6]. Mário P. Véstias and Horácio C. Neto, "Parallel Decimal Multipliers Using Binary Multipliers", VI Southern Programmable Logic Conference (SPL), March 2010.

- [7]. Abdoreza Pishvaie et al, "Redesigned CMOS (4; 2) compressor for fast binary multipliers", Canadian Journal of Electrical and Computer Engineering, Volume: 36, Issue: 3, pp. 111 – 115, January – 2014.

- [8]. Sunil Kumar Ojha, O.P. Singh, G.R. Mishra, and P.R. Vaya, "Analysis and Design of Single Ended SRAM Cell for Low-Power Operation", IEEE 11th Conference on Industrial & Information Systems, IIT Roorkee, Year – 2016.

- [9]. Sunil Kumar Ojha, O.P. Singh, G.R.Mishra, and P.R. Vaya, "Analysis of SRAM Cell for Low Power Operation and Its Noise Margin", International Conference on VLSI, Communication and Signal Processing (VCAS), MNNIT Allahabad, Year – 2018.

- [10]. L. Wang and I. Hartimo, "Systolic Array for Binary Multiplier", International Symposium on Speech, Image Processing and Neural Networks, April 1994.

- [11]. Nicola Petra et al, "Truncated Binary Multipliers with Variable Correction and Minimum Mean Square Error", IEEE Transactions on Circuits and Systems I: Regular Papers, Volume: 57, Issue: 6, pp. 1312 – 1325, June 2010.

- [12]. Sunil Kumar Ojha, O.P. Singh, G.R. Mishra, and P.R. Vaya, "Design of DRAM having Dummy Cell Sensing Structure", IEEE Conference on Recent Advances in Electronics & Computer Engineering, IIT Roorkee, Year – 2015.

- [13]. Kirk D. Lamb, "Use of Binary Decision Diagrams in the Modelling and Synthesis of Binary Multipliers", IEEE International ASIC Conference and Exhibit, August 2002.

- [14]. Aryan Saed, "VLSI Improvements in a Binary Multiplier based on Analog Digits", Conference Record of the Thirty-Third Asilomar Conference on Signals, Systems, and Computers, August 2002.